خب بذارین براتون یه موضوع جالب از دنیای سختافزار و هوش مصنوعی تعریف کنم! یه چیزی تازگیها مطرح شده به اسم EvoVerilog که خیلیها رو هیجانزده کرده. اگه با Verilog آشنا نیستین، این یه زبان برنامهنویسی خاص برای توصیف سختافزار هست؛ یعنی باهاش میشه مدارها و چیپستها رو به صورت نرمافزاری تعریف کرد تا بعداً بسازنشون.

حالا داستان چیه؟ تا قبل از این، برای نوشتن کد Verilog، کلی زحمت و وقت و دقت لازم بود، چون واقعاً کار پیچیدهایه و یه اشتباه کوچیک میتونه همه چی رو بریزه به هم. خیلی از روشهایی که هوش مصنوعی میخواست این کار رو راحتتر کنه، به یه مشکل میخورن: معمولاً لازمه آدمها وسطش دخالت کنن یا باید کلی داده خاص به مدل بدن و مدل رو، اصطلاحاً، fine-tune کنن (یعنی یه جوری روی دادههای جدید آموزش بدن دوباره). این کارها واسه اتوماسیون و مقیاسپذیریش اصلاً خوب نیست.

تازه یه سری آدم باهوش اومدن روشهای جستجوی تکراری و هوشمندانه گذاشتن که شاید بدون نیاز به کمک انسان بشه کلی مدل طراحی کرد؛ اما بازم یا طراحیهایی که به دست میاد اونقدر متنوع نیست یا شاید حتی توی بعضی موارد یه روش ساده مثل چند بار پرسیدن مدل هوش مصنوعی، نتیجه بهتری بده!

حالا EvoVerilog دقیقاً همینجاست که میدرخشه. این ابزار یه ایده باحال داره: میاد قابلیت تحلیل و استدلال مدلهای زبانی بزرگ (Large Language Models یعنی همون ChatGPTها که بهشون گفتن LLM) رو با یه چیز دیگه پیوند میزنه به اسم الگوریتمهای تکاملی. بذار یه توضیح بدم: الگوریتم تکاملی، سیستمیه که مثل فرایند تکامل تو طبیعت کار میکنه – یه سری راهحل مختلف رو توی جمعیت نگه میداره، بهترینها رو انتخاب میکنه و کمکم اونها رو بهتر و بهتر میکنه.

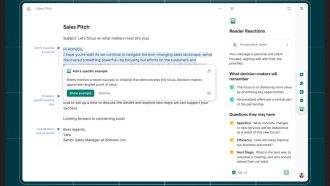

اینجا EvoVerilog یه سیستم چندهدفی و مبتنی بر جمعیت پیاده کرده (یعنی دنبال هدفای مختلف میره و به طور همزمان کلی راهحل متنوع میسازه)، واسه همین آدمها نباید هی دخالت کنن. واسه مقایسه، محققها دو تا بنچمارک معروف ساختن (بنچمارک یعنی مجموعهای از تستها برای مقایسه عملکرد روشها)، یکی به اسم VerilogEval-Machine و یکی دیگه VerilogEval-Human. مدل EvoVerilog تونست توی این تستها به نمره pass@10 معادل ۸۹.۱ در بنچمارک ماشینی و ۸۰.۲ در بنچمارک انسانی برسه، که واقعاً عالیه!

جالبتر اینکه EvoVerilog فقط یه راهحل تولید نمیکنه، بلکه همزمان چند مدل مختلف و سالم از کد Verilog میده که هرکدوم استفادهشون میتونه تو بهینه کردن منابع سختافزاری مختلف باشه. یعنی نه تنها پیچیدگی رو کمتر میکنه، تنوع طراحیها رو هم بالا میبره، که خیلی باحاله.

خلاصه بخوام بگم، این EvoVerilog اومده کلی کار سخت و زمانبر طراحی سختافزار رو خیلی راحتتر و اتوماتیک کنه، بدون اینکه حتماً آدمها وسطش باشن یا لازم باشه برای هر نیاز یه بار هوش مصنوعی رو تربیت کنن. آینده طراحی سختافزار با این چیزا خیلی سریعتر و جذابتر میشه!

منبع: +